ULPMark®-CoreProfile

Overview

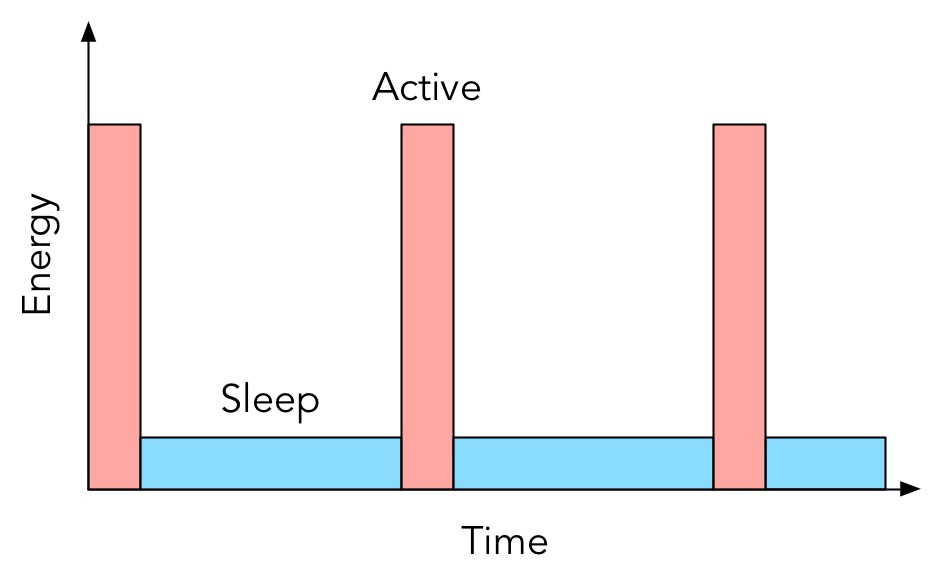

The ULPMark-CoreProfile benchmark focuses on the MCU’s core, specifically the energy cost in sleep, and the transition to and from active mode. This benchmark utilizes a common set of workloads that are portable across 8-, 16-, and 32-bit microcontrollers. The Core Profile runs on a one-second duty cycle combining these workloads with an extended period of inactivity to enable the use of microcontroller low-power modes. Please refer to the FAQ for more information on the active workload.

While the active portion of the benchmark is only running for ~3% of the total runtime, it requires data to be saved during deep-sleep through the use of "retention RAM". Since it is rare that a sleepy edge node would clear its RAM after every sleep cyle, the exit- and enter-costs of retention RAM illustrate the true energy cost of sleep modes. There's more to it than just a datasheet number!

During the active portion of the test, the benchmark does the following:

- Generate 20 GPIO pulses

- Perform an 8-bit linear interpolation

- Perform a 16-bit integration (filter)

- Compute a 7-segment LCD binary conversion (saving state)

- Search for a substring in a string

- Perform a small bubble-sort

- Permute the bits of a string based on input and previous state

Framework Update

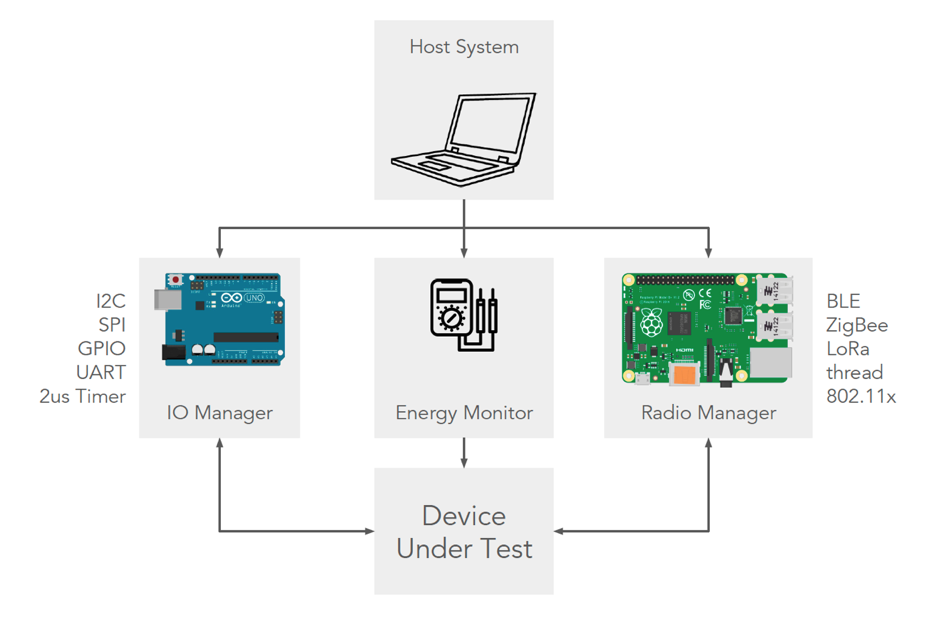

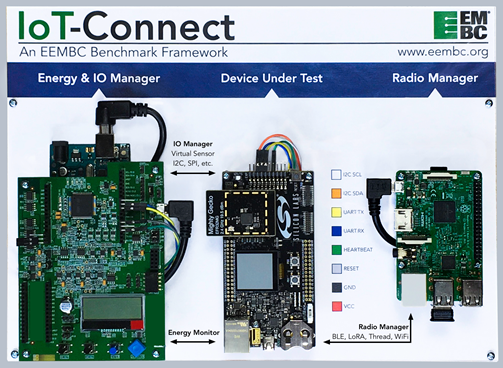

ULPMark has been redesigned since it's first release in 2014. It now works with the EEMBC benchmark framework, the same one used by IoTMark and SecureMark, with a super-thin API that enables any MCU to execute next generation EEMBC benchmarks. The STMicroelectronics PowerShield provides the backbone of the framework's energy measurement, with sub-100nJ accuracy on your desktop for around US$100.

The framework used for ULPMark creates an extensible framework for probing an embedded system. Block diagram (left), actual implementation (right). Click to enlarge. Note that for ULPMark-CP and ULPMark-PP, the Radio Manager and IO Manager are not required.

Obtaining the Benchmark

In order to run the benchmark and submit scores, you must obtain a license.